# **Intel Joule Module**

**Expansion Board Hardware Guide**

December 2016

**Revision 1.0**

Introduction

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

This document contains information on products in the design phase of development.

All products, platforms, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice. All dates specified are target dates, are provided for planning purposes only and are subject to change.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See www.intel.com/products/processor\_number for details.

Intel, Intel Joule and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2016, Intel Corporation. All rights reserved.

# **Table of Contents**

| 1 | Intro | duction                                                                                            | 9  |

|---|-------|----------------------------------------------------------------------------------------------------|----|

|   | 1.1   | Scope                                                                                              | 9  |

|   | 1.2   | Acronyms and terminology                                                                           | 9  |

|   | 1.3   | References                                                                                         | 10 |

|   | 1.4   | Part numbers                                                                                       | 11 |

| 2 | High  | Level Description                                                                                  | 12 |

|   | 2.1   | Intel Joule module to expansion board interface                                                    | 12 |

|   | 2.2   | Expansion board feature highlights                                                                 | 12 |

|   | 2.3   | Block diagram                                                                                      | 13 |

| 3 | Expar | nsion Board Interfaces                                                                             | 15 |

|   | 3.1   | Buttons, jumpers, and LEDs                                                                         |    |

|   |       | 3.1.1 Power button (SW2)                                                                           |    |

|   |       | 3.1.2 DNX boot button (SW3)                                                                        |    |

|   |       | 3.1.3 General purpose button (SW1)                                                                 |    |

|   | 3.2   | Boot-option strapping jumpers (J14)                                                                |    |

|   | 3.3   | Power LED (CR9)                                                                                    |    |

|   | 3.4   | General purpose LEDs                                                                               |    |

| 4 | Break | cout Connectors                                                                                    |    |

|   |       | 4.1.1 Breakout connector J12                                                                       |    |

|   |       | 4.1.2 Breakout connector J13                                                                       | 24 |

| 5 | Powe  | ring the Expansion Board                                                                           |    |

|   | 5.1   | DC power jack input (J4)                                                                           |    |

|   | 5.2   | USB Type-C power input (J7)                                                                        |    |

|   | 5.3   | Battery path                                                                                       |    |

|   | 5.4   | Power-on and shut-down signaling                                                                   |    |

|   | 5.5   | Control signal termination and conditioning                                                        | 28 |

| 6 | Powe  | r Delivery Subsystem                                                                               | 29 |

|   | 6.1   | Power delivery overview                                                                            | 29 |

|   | 6.2   | Power supply sequencing                                                                            |    |

|   | 6.3   | Voltage regulators and load switches                                                               |    |

|   |       | 6.3.1 +5 Boost regulator (U21)                                                                     |    |

|   |       | 6.3.2 + 3.3 Boost regulator (U27)                                                                  |    |

|   |       | <ul> <li>6.3.3 +1.8 Buck regulator (EU5)</li> <li>6.3.4 USB load switches (U17 and EU3)</li> </ul> |    |

|   |       | 6.3.5 Module sourced power supplies (+VDD1 and +VDD3)                                              |    |

|   |       | 6.3.6 Module sourced power supplies                                                                |    |

|   | 6.4   | RTC Backup battery                                                                                 |    |

#### Introduction

|    | 6.5 Maximum current draw                                                                            |    |

|----|-----------------------------------------------------------------------------------------------------|----|

|    | 6.6 Termination and conditioning                                                                    |    |

| 7  | Clocks                                                                                              |    |

|    | 7.1 19.2 MHz system clock                                                                           |    |

|    | 7.2 32.768 kHz real time clock                                                                      |    |

|    | 7.3 Clock signal termination and conditioning                                                       |    |

|    | 7.3.1 Example using CLK_19P2M_LS signal                                                             |    |

| 8  | HDMI Subsystem                                                                                      |    |

|    | 8.1 Micro-HDMI* (Type-D) connector pinout                                                           |    |

| 9  | SD Card Subsystem                                                                                   |    |

| 10 |                                                                                                     |    |

| 10 | 10.1 GPIO signal termination and conditioning                                                       |    |

|    | 10.1.1 Example using GPIO signal                                                                    |    |

| 11 |                                                                                                     |    |

| 11 | I2S Interface<br>11.1 I2S level transitions                                                         |    |

|    | <ul><li>11.1 I2S level transitions</li><li>11.2 Audio signal termination and conditioning</li></ul> |    |

|    |                                                                                                     |    |

| 12 |                                                                                                     |    |

|    | 12.1 DMIC signal termination and conditioning                                                       |    |

| 13 | SPI interface                                                                                       |    |

|    | 13.1 SPI level transitions                                                                          |    |

|    | 13.2 SPI strapping for SD card boot                                                                 |    |

|    | 13.3 SPI signal termination and conditioning                                                        |    |

| 14 | UART Interfaces                                                                                     |    |

|    | 14.1 UART level translation on the expansion board                                                  |    |

|    | 14.2 UART Signal Termination and Conditioning                                                       |    |

| 15 | USB Subsystem                                                                                       |    |

|    | 15.1 USB Type-C with OTG (J7)                                                                       |    |

|    | 15.1.1 USB Type-C inverted cable mux (EU4)                                                          |    |

|    | 15.3 USB 3.0 Type-A (J6)                                                                            |    |

|    | 15.4 USB electrical characteristics                                                                 |    |

|    | 15.4.1 USB Controllers                                                                              |    |

| 16 |                                                                                                     |    |

|    | 16.1 PWM signal termination and conditioning                                                        |    |

| 17 | Configuration EEPROM                                                                                | 57 |

| 18 | Mechanical and Environmental                                                                        |    |

|    | 18.1 Mechanical dimensions                                                                          |    |

|    |                                                                                                     |    |

#### Introduction

|    | 18.2  | Operating electrostatic discharge (ESD) | 59 |

|----|-------|-----------------------------------------|----|

|    | 18.3  | Temperature range                       | 59 |

|    | 18.4  | Cooling fan (J17)                       | 59 |

|    | 18.5  | Thermal profiling and enclosures        | 59 |

| 19 | Debug | and Troubleshooting                     | 60 |

|    | 19.1  | Serial debug port (J9)                  | 60 |

|    | 19.2  | Troubleshooting                         | 60 |

|    |       |                                         |    |

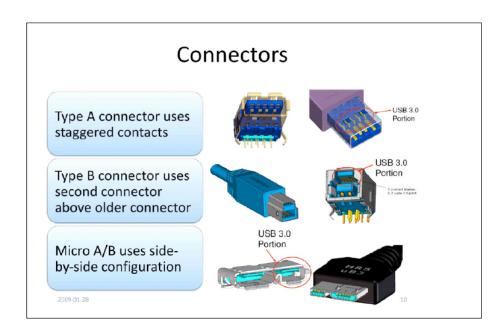

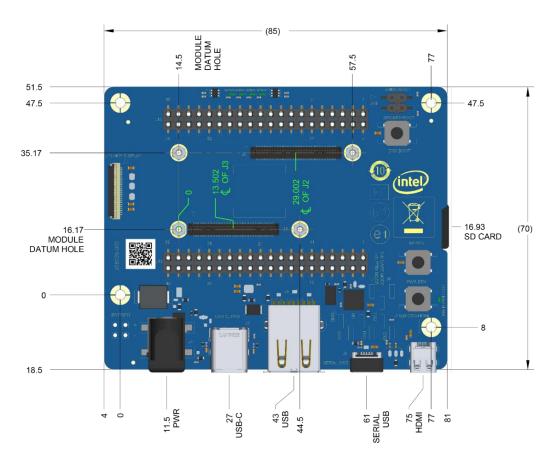

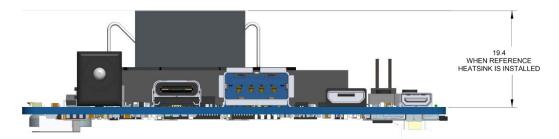

| Figure 2. Expansion board block diagram – module connector J3 to J13 connector       14         Figure 3. Intel Joule expansion board - top view       15         Figure 4. Intel Joule expansion board - bottom view       16         Figure 5. Intel Joule expansion board buttons       17         Figure 6. Expansion board boot-strapping jumpers (J14)       19         Figure 7. Intel Joule expansion board LEDs       20         Figure 8. Expansion board power delivery block diagram       29         Figure 9: Power on timing sequence (cold boot)       30         Figure 10: Test setup to determine the termination and conditioning values       34         Figure 11: Example pullup resistor for 1.8 V pullup voltage       38         Figure 13: USB connector types       55         Figure 14. Expansion board key dimensions – top view       58         Figure 15. Expansion board key dimensions – side view       59 | Figure 1. Expansion board block diagram – module connector J2 to J12 breakout connector | 13 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----|

| Figure 4. Intel Joule expansion board - bottom view16Figure 5. Intel Joule expansion board buttons17Figure 6. Expansion board boot-strapping jumpers (J14)19Figure 7. Intel Joule expansion board LEDs20Figure 8. Expansion board power delivery block diagram29Figure 9: Power on timing sequence (cold boot)30Figure 10: Test setup to determine the termination and conditioning values34Figure 11: Example pullup resistor for 1.8 V pullup voltage38Figure 13: USB connector types55Figure 14. Expansion board key dimensions – top view58                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 2. Expansion board block diagram – module connector J3 to J13 connector          | 14 |

| Figure 5. Intel Joule expansion board buttons17Figure 6. Expansion board boot-strapping jumpers (J14)19Figure 7. Intel Joule expansion board LEDs20Figure 8. Expansion board power delivery block diagram29Figure 9: Power on timing sequence (cold boot)30Figure 10: Test setup to determine the termination and conditioning values34Figure 11: Example pullup resistor for 1.8 V pullup voltage38Figure 12. Example pullup resistor on a 3.3 voltage44Figure 13: USB connector types55Figure 14. Expansion board key dimensions – top view58                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 3. Intel Joule expansion board - top view                                        | 15 |

| Figure 6. Expansion board boot-strapping jumpers (J14)19Figure 7. Intel Joule expansion board LEDs20Figure 8. Expansion board power delivery block diagram29Figure 9: Power on timing sequence (cold boot)30Figure 10: Test setup to determine the termination and conditioning values34Figure 11: Example pullup resistor for 1.8 V pullup voltage38Figure 12. Example pullup resistor on a 3.3 voltage44Figure 13: USB connector types55Figure 14. Expansion board key dimensions – top view58                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 4. Intel Joule expansion board - bottom view                                     | 16 |

| Figure 7. Intel Joule expansion board LEDs20Figure 8. Expansion board power delivery block diagram29Figure 9: Power on timing sequence (cold boot)30Figure 10: Test setup to determine the termination and conditioning values34Figure 11: Example pullup resistor for 1.8 V pullup voltage38Figure 12. Example pullup resistor on a 3.3 voltage44Figure 13: USB connector types55Figure 14. Expansion board key dimensions – top view58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 5. Intel Joule expansion board buttons                                           | 17 |

| Figure 8. Expansion board power delivery block diagram29Figure 9: Power on timing sequence (cold boot)30Figure 10: Test setup to determine the termination and conditioning values34Figure 11: Example pullup resistor for 1.8 V pullup voltage38Figure 12. Example pullup resistor on a 3.3 voltage44Figure 13: USB connector types55Figure 14. Expansion board key dimensions – top view58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 6. Expansion board boot-strapping jumpers (J14)                                  | 19 |

| Figure 9: Power on timing sequence (cold boot)30Figure 10: Test setup to determine the termination and conditioning values34Figure 11: Example pullup resistor for 1.8 V pullup voltage38Figure 12: Example pullup resistor on a 3.3 voltage44Figure 13: USB connector types55Figure 14. Expansion board key dimensions – top view58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 7. Intel Joule expansion board LEDs                                              | 20 |

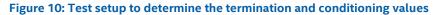

| Figure 10: Test setup to determine the termination and conditioning values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 8. Expansion board power delivery block diagram                                  | 29 |

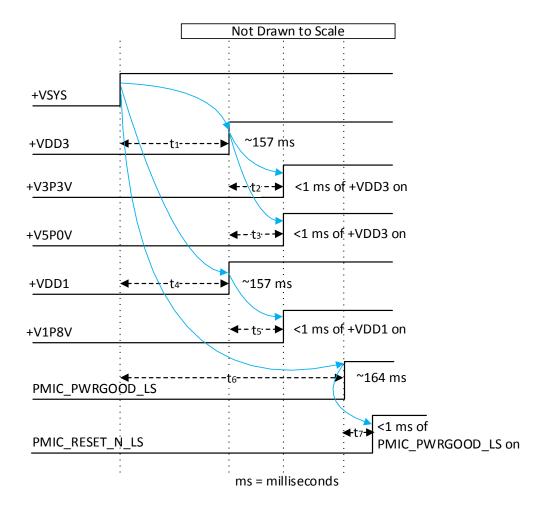

| Figure 11: Example pullup resistor for 1.8 V pullup voltage38Figure 12. Example pullup resistor on a 3.3 voltage44Figure 13: USB connector types55Figure 14. Expansion board key dimensions – top view58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 9: Power on timing sequence (cold boot)                                          | 30 |

| Figure 12. Example pullup resistor on a 3.3 voltage44Figure 13: USB connector types55Figure 14. Expansion board key dimensions – top view58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 10: Test setup to determine the termination and conditioning values              | 34 |

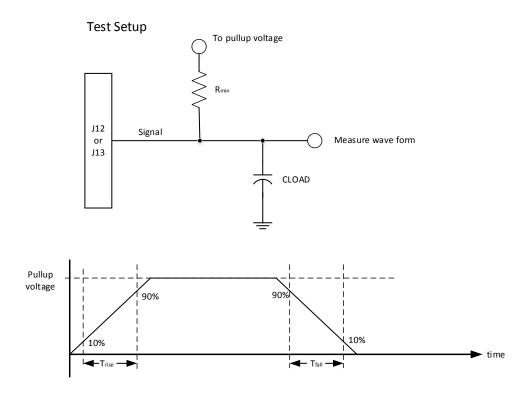

| Figure 13: USB connector types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 11: Example pullup resistor for 1.8 V pullup voltage                             | 38 |

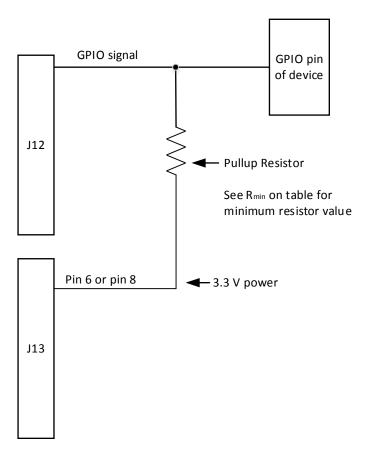

| Figure 13: USB connector types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 12. Example pullup resistor on a 3.3 voltage                                     | 44 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |    |

| Figure 15 Expansion hoard key dimensions – side view 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 14. Expansion board key dimensions - top view                                    | 58 |

| ingure 15. Expansion board key amensions - side view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 15. Expansion board key dimensions – side view                                   | 59 |

| Table 1. Expansion board features                                     |    |

|-----------------------------------------------------------------------|----|

| Table 2. General purpose LED mapping                                  |    |

| Table 3. Breakout connector J12 pinout                                |    |

| Table 4. Breakout connector J13 pinout                                |    |

| Table 5. DC power jack electrical specifications                      |    |

| Table 6. USB type-C power input electrical specifications             |    |

| Table 7. Control signal level translation termination recommendations |    |

| Table 8. Power supplies electrical specifications                     |    |

| Table 9. Maximum current draw +V1P8V, +V3P3V, and +V5P0V              |    |

| Table 10. 19.2 MHz clock DC specifications                            |    |

| Table 11. 19.2 MHz clock AC specifications                            |    |

| Table 12. RTC clock DC specifications (1.8 volt pullup)               |    |

| Table 13. RTC clock AC specifications (1.8 volt pullup)               |    |

| Table 14. RTC clock DC specifications (3.3 volt pullup)               |    |

| Table 15. RTC clock AC specifications (3.3 volt pullup)               |    |

| Table 16.Clock signal level translation termination recommendations   |    |

| Table 17. Micro-HDMI (type-D) connector pinout                        |    |

| Table 18. Micro SD card connector pinout                              | 41 |

| Table 19. GPIO mapping table                                          |    |

| Table 20. GPIO signal level translation termination recommendations   |    |

| Table 21. I2S Mapping to breakout connectors                          |    |

| Table 22. SPI signal level translation termination recommendations    |    |

| Table 23. DMIC signal level translation termination recommendations   |    |

| Table 24. SPI mapping to breakout connectors                          |    |

| Table 25. SPI signal level translation termination recommendations    |    |

| Table 26. UART mapping to breakout connectors                         |    |

| Table 27. UART signal level translation termination recommendations   | 51 |

| Table 28. USB type-C connector pinout                                 |    |

| Table 29. USB 3.0 type-A connector pinout                             |    |

| Table 30. USB connect or disconnect scheme – connector dependent      | 55 |

| Table 31. PWM signal level translation termination recommendations    |    |

| Table 32. Fan connector pin assignments                               |    |

| Revision<br>Number | Description     | Revision Date |

|--------------------|-----------------|---------------|

| 1.0                | Initial Release | December 2016 |

|                    |                 |               |

# 1.1 Scope

This document describes the devices and circuitry on the expansion board for the Intel<sup>®</sup> Joule<sup>™</sup> compute module.

The expansion board is a development platform for prototyping and exploring application solutions powered by the Intel Joule module. As such, certain devices and features might not function, depending on the firmware installed, the operating system installed, and devices attached to ports and connectors.

Scope of this document is limited to functions performed by the expansion board.

Consult datasheets from the original device manufacturer and available information provided by the operating system vendors for software environments to fully understand what is available from the original device manufacture.

### 1.2 Acronyms and terminology

| Term or<br>Acronym | Description or Definition                                                          |  |

|--------------------|------------------------------------------------------------------------------------|--|

| AC                 | Alternating Current                                                                |  |

| BIOS               | Basic Input Output System                                                          |  |

| сс                 | Configuration Channel. Relates to USB Type-C connectors.                           |  |

| CSE                | Converged Security Engine. Responsible for retrieving and validating all firmware. |  |

| DC                 | Direct Current                                                                     |  |

| EEPROM             | Electrically Erasable Programmable Read-Only Memory                                |  |

| eMMC               | Embedded MultiMedia Card                                                           |  |

| FFC                | Flexible Flat Cable                                                                |  |

| GPIO               | General purpose input / output                                                     |  |

| HDMI*              | High Definition Multimedia Interface                                               |  |

| 12C                | Inter-IC Bus; also known as the "I-squared-C bus"                                  |  |

| 125                | Integrated Interchip Sound; also known as the "I-squared-S bus"                    |  |

| Term or<br>Acronym                                                                                                                                                   | Description or Definition                                 |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| IC                                                                                                                                                                   | Integrated Circuit                                        |  |

| LED                                                                                                                                                                  | Light Emitting Diode                                      |  |

| LCD                                                                                                                                                                  | Liquid Crystal Display                                    |  |

| NC                                                                                                                                                                   | No Connect. Signal is not used or is to be left floating. |  |

| Net Names Signals on the printed circuit board are often referred to by their signal, or net na<br>The name of a signal often changes when passing through a device. |                                                           |  |

| OTG On-The-Go; specifically related to the USB On-The-Go technology. OTG po required to provide a minimum power to devices.                                          |                                                           |  |

| OS                                                                                                                                                                   | Operating System                                          |  |

| РСВ                                                                                                                                                                  | Printed Circuit Board                                     |  |

| PWM                                                                                                                                                                  | Pulse Width Modulation                                    |  |

| SD Card                                                                                                                                                              | Secure Digital card                                       |  |

| SoC                                                                                                                                                                  | System on Chip                                            |  |

| SPI                                                                                                                                                                  | Serial Peripheral Interface                               |  |

| UART                                                                                                                                                                 | Universal Asynchronous Receiver Transmitter               |  |

| USB                                                                                                                                                                  | Universal Serial Bus                                      |  |

# 1.3 References

| Document                                   | Document Location                                                          |  |

|--------------------------------------------|----------------------------------------------------------------------------|--|

| Intel <sup>®</sup> Joule™ Module Datasheet | https://software.intel.com/en-us/articles/intel-joule-<br>module-datasheet |  |

| Intel® Joule™ Expansion Board              | https://software.intel.com/en-us/articles/intel-joule-                     |  |

| Schematics and BOM                         | expansion-board-schematic                                                  |  |

| Intel® Joule™ Module User Guide            | https://software.intel.com/en-us/intel-joule-getting-<br>started           |  |

| Mechanical Descriptor for Intel® Joule™    | http://www.intel.com/content/www/us/en/support/boa                         |  |

| Platform                                   | rds-and-kits/000022366.html                                                |  |

| Thermal Management Overview for the        | http://www.intel.com/content/www/us/en/support/boards-                     |  |

| Intel® Joule™ Module Developer Kit         | and-kits/000023095.html                                                    |  |

| Document                            | Document Location                                     |

|-------------------------------------|-------------------------------------------------------|

| Troubleshooting and FAQ – Using the | https://software.intel.com/en-us/troubleshooting-and- |

| Intel® Joule™ development platform  | faq-for-joule                                         |

# 1.4 Part numbers

The part numbers listed throughout this document are the specific parts on the Intel Joule expansion board at the time of publication. Those parts may in the future be replaced with equivalent parts from other manufacturers.

§

# 2.1 Intel Joule module to expansion board interface

The module interfaces to the expansion board through twin, high-density 100-pin connectors, J2 and J3, which respectively mate to J6 and J7 on the expansion board.

*Caution:* The board-to-board connectors are rated for a maximum of 30 socketing cycles. You risk signal degradation after seating and removing the compute module more than 30 times.

### 2.2 Expansion board feature highlights

The expansion board provides two 40-pin ( $0.1 \times 0.1$  pitch) breakout connectors that expose various features, power signals, and communication buses of the compute module. The expansion board also provides some standard, physical interface ports.

Some signals to and from the module are routed directly to the breakout connectors (J12 and J13) and physical ports; others receive level-conditioning when in transit on the board.

| Component             | Description                                                                                                                                                                                       |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power input           | Physical input connector, fused for current protection                                                                                                                                            |  |

| Physical interfaces   | Physical connectors for a number of module interfaces are provided by the expansion board:                                                                                                        |  |

|                       | • Micro USB Type A                                                                                                                                                                                |  |

|                       | • USB Type-C                                                                                                                                                                                      |  |

|                       | <ul> <li>Micro USB Type-B for serial debug (UART bridge)</li> </ul>                                                                                                                               |  |

|                       | • Micro HDMI*                                                                                                                                                                                     |  |

| Level translation     | The expansion board provides open collector type level<br>translation and requires pullups on the attached mezzanine<br>cards to the end-user's desired voltage levels, not to exceed<br>3.3 VDC. |  |

| Voltage regulation    | Expansion board provides additional voltage regulators to enable the level transition and conditioning devices.                                                                                   |  |

| Configuration jumpers | Header pins provide the ability to disable booting from the SD Card or from the eMMC image on the module.                                                                                         |  |

#### Table 1. Expansion board features

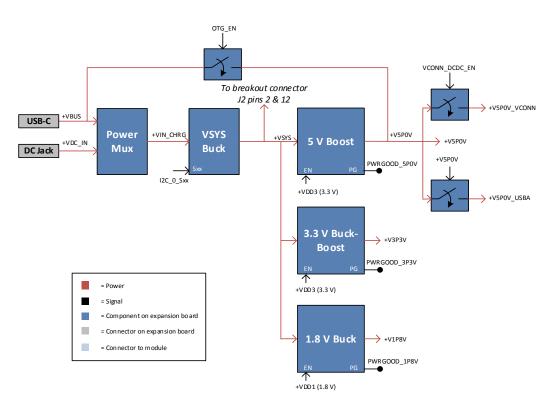

## 2.3 Block diagram

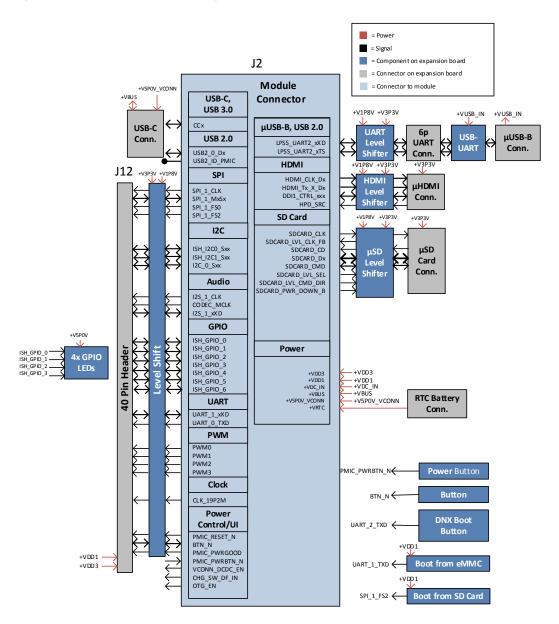

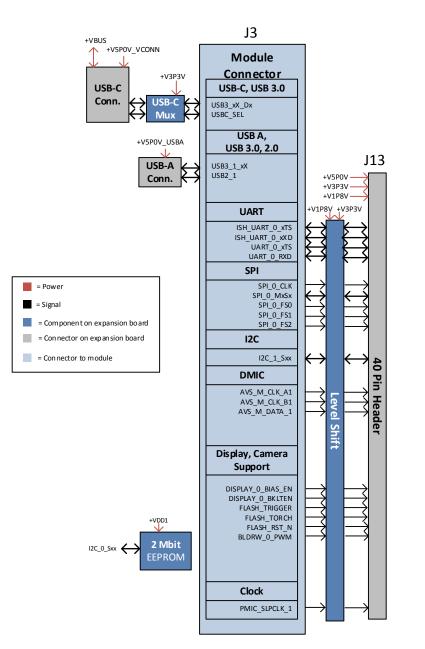

Figure 1 and Figure 2 show the high-level block diagram for the expansion board in two parts for better readability.

Figure 1. Expansion board block diagram - module connector J2 to J12 breakout connector

#### Figure 2. Expansion board block diagram - module connector J3 to J13 connector

§

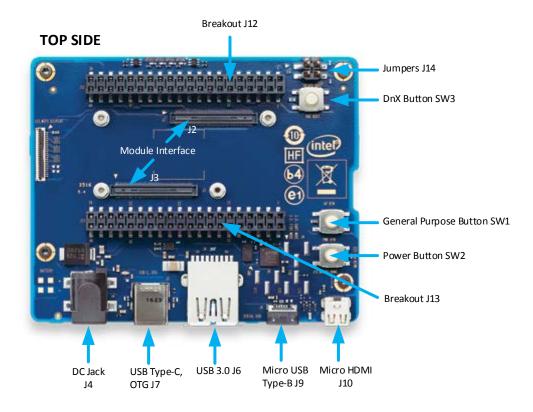

This section provides a visual overview of the ports, connectors, and mechanical interfaces of the Intel Joule expansion board; shown without an Intel Joule module installed.

#### Figure 3. Intel Joule expansion board - top view

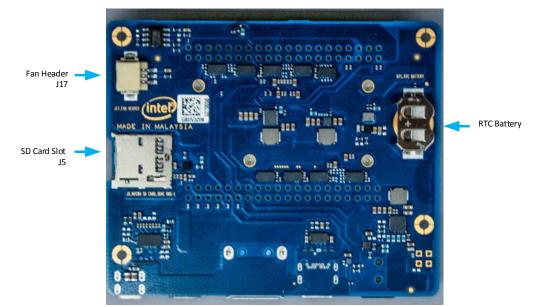

#### Figure 4. Intel Joule expansion board - bottom view

#### **BOTTOM SIDE**

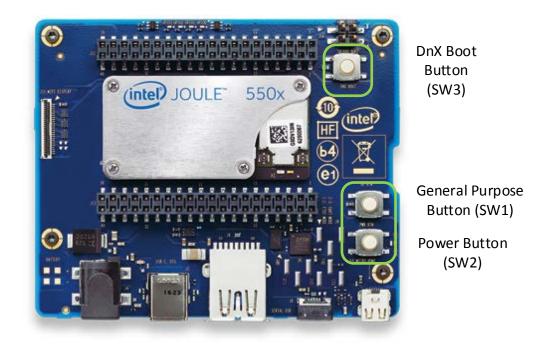

## 3.1 Buttons, jumpers, and LEDs

The Intel Joule expansion board contains three buttons. Two of the three buttons have predefined operation, while the third button is user defined. The three buttons are titled:

- Power Button (PWR BTN)

- DNX Boot Button (DNX BOOT)

- General Purpose Button (GP BTN)

Refer to Figure 5 for the locations of the buttons.

#### Figure 5. Intel Joule expansion board buttons

### 3.1.1 Power button (SW2)

The power button is connected to the PMIC\_PWRBTN\_N signal of the module. When the button is pressed, the PMIC\_PWRBTN\_N signal is pulled to ground, driving the PMIC\_PWRBTN\_N signal to a low state. When the button is released, the PMIC\_PWRBTN\_N signal is pulled high, to +VSYS in the module.

**Note:** The low time durations of the PMIC\_PWRBTN\_N signal result in various actions on the module. Refer to the Intel<sup>®</sup> Joule<sup>™</sup> Module Datasheet for specific information and usage for the PMIC\_PWRBTN\_N signal and the resulting actions.

### 3.1.2 DNX boot button (SW3)

The DNX boot button is connected to the UART\_2\_TXD signal of the module. When the button is pressed, the UART\_2\_TXD signal is pulled high through a 100 $\Omega$  resistor to +VDD1 (1.8 volts). When the button is released, the UART\_2\_TXD signal is left floating, but relies on a 20k $\Omega$  internal pull-down within the module SoC to insure a low-level signal.

The DNX boot button is used to initiate a BIOS programming cycle when pressed and held during a power-up cycle. At the rising edge of the module's PMIC\_PWRGOOD signal (for example during a power-up cycle), the UART\_2\_TXD is sampled by the module SoC. If the UART\_2\_TXD is sampled as a high signal, then the SoC initiates a BIOS update from the USB Type-C port. Similarly, if the UART\_2\_TXD signal is sampled as a low signal (for example DNX boot button released) on the rising edge of PMIC\_PWRGOOD, then a BIOS update is not initiated and the boot process continues normally.

### 3.1.3 General purpose button (SW1)

The general purpose button is available to be defined by the software developer. It is connected to the BTN\_N signal of the module. When the button is pressed, the BTN\_N signal is shorted to ground, driving the BTN\_N signal to a low state. When the button is released, the BTN\_N signal is pulled high, to +VDD1 (1.8 volts).

Refer to the Intel Joule Module Datasheet for the function mapping of the BTN\_N signal.

### **3.2 Boot-option strapping jumpers (J14)**

Jumper block J14 provides the ability to selectively enable boot sources for the expansion board, specifically, the ability to enable booting from the SD card or from eMMC.

Refer to Figure 6 for the locations of the jumper block.

The jumper must be installed prior to a power-up of the expansion board, as the state of the jumpers is sampled by the module at the rising edge of the PMIC\_PWRGOOD signal, during the power-up process.

- Placing a jumper across pins 1 and 2 of J14 enables booting from eMMC.

- Placing a jumper across pins 3 and 4 of J14 enables booting from the SD card.

*Note:* The default configuration is no jumpers installed.

#### Figure 6. Expansion board boot-strapping jumpers (J14)

Top pair: enable eMMC boot if jumpered Bottom pair: enable SD card boot if jumpered

NOTE: BIOS defines boot order

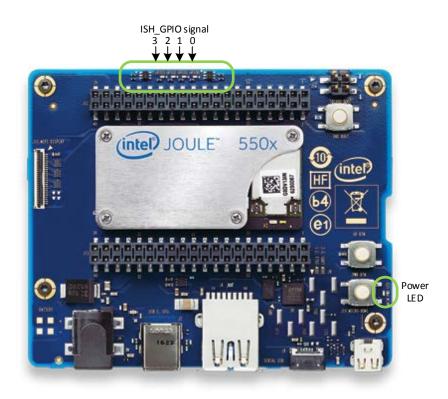

### 3.3 Power LED (CR9)

A main power LED is located near the power switch (SW2) (refer to Figure 7 for the location) and is enabled when all expansion board power rails are stabilized and a general power good state is achieved.

### 3.4 General purpose LEDs

There are four general purpose LEDs located in the upper center area of the expansion board. Refer to Figure 7 for the location of the LEDs. The LED is turned on when the related GPIO signal is high, regardless of whether the GPIO is configured as an input or an output.

In addition to being user programmable, these LEDs are used by the BIOS to indicate progression of the boot process or other information. All four LEDs are illuminated when BIOS passes code execution to the operating system (OS). Depending on the BIOS build, these GPIO lines can be left high or low, and set as either input or output. See the BIOS release notes for additional information.

#### Table 2. General purpose LED mapping

| LED Reference<br>Designator | Net Name   | Breakout Pin # | Linux* GPIO |

|-----------------------------|------------|----------------|-------------|

| GPIO0                       | ISH_GPIO_0 | J12-35         | 337         |

| GPIO2                       | ISH_GPIO_1 | J12-33         | 339         |

| GPIO1                       | ISH_GPIO_2 | J12-31         | 338         |

| GPIO3                       | ISH_GPIO_3 | J12-29         | 340         |

Figure 7. Intel Joule expansion board LEDs

§

# 4 Breakout Connectors

The Intel Joule expansion board contains two forty-pin connectors, each having a 2x20 configuration at 0.1-inch spacing, to enable external circuit connections.

These connectors are referred to as the breakout connectors. They expose several interfaces and module signals required to develop complete systems.

These breakout connectors provide access to the following interfaces:

- Two SPI ports

- Three UARTs

- Five I2C ports

- One I2S port

- Four PWM interfaces

- Eight dedicated GPIO signals, and seven user programmable GPIO signals

- Two digital microphone inputs

- Various voltage rails and power signals

The expansion board provides open collector type level translation (shifting) of the module 1.8 VDC I/O lines and requires pullups on the attached mezzanine cards to the end-user's desired voltage levels typically used in the development phase, not to exceed 3.3 VDC. Details of any level translation, conditioning or buffering applied by the expansion board are found in the respective sections for those specific interfaces where such is applied.

### 4.1.1 Breakout connector J12

The table below provides the pin assignment, signal name, and description for the signals on the breakout connector J12. The default breakout usage refers to the vantage point of the expansion board. For example, the SPI\_1\_MISO\_LS signal originates in the breakout board and is delivered to the expansion board, therefore it is an input.

These signals are mapped by various operating systems in different ways. These mappings can change over time and with BIOS updates. This table does not address those mappings. Refer to the Intel Joule module website for current mappings for supported operating systems.

#### Table 3. Breakout connector J12 pinout

| J12<br>Pin | Net Name at<br>Breakout    | Signal Description                                                                                                                                                                                                                                                                                                                     | Default<br>Breakout<br>Usage | Module<br>Pin |

|------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------|

| 1          | GPIO_22_LS                 | General purpose input/output                                                                                                                                                                                                                                                                                                           | Input                        | J2 - 94       |

| 2          | SPI_1_MISO_LS              | SPI port 1 receive data.                                                                                                                                                                                                                                                                                                               | Input                        | J2 - 63       |

| 3          | PMIC_RESET_N               | Active low output from the expansion<br>board to the module that controls the<br>power state of the module and, by<br>extension, the expansion board, see the<br>Intel <sup>®</sup> Joule <sup>™</sup> Module Datasheet for how<br>the PMIC_PWRBTN_N signal controls the<br>module power state based on duration of<br>the low signal. | Input                        | J2 - 9        |

| 4          | SPI_1_MOSI_LS              | SPI port 1 transmit data                                                                                                                                                                                                                                                                                                               | Output                       | J2 - 51       |

| 5          | CLK_19P2M_LS               | 19.2 MHz clock                                                                                                                                                                                                                                                                                                                         | Output                       | J2 - 71       |

| 6          | SPI_1_FS0_LS               | SPI port 1 slave select 0                                                                                                                                                                                                                                                                                                              | Output                       | J2 - 55       |

| 7          | UART_0_TXD_LS <sup>1</sup> | UART port 0 transmit data, hardware strap with reserved functionality                                                                                                                                                                                                                                                                  | Output                       | J3 – 15       |

| 8          | SPI_1_FS2_LS               | SPI port 1 slave select 2, hardware strap<br>with disable boot from SD card<br>functionality                                                                                                                                                                                                                                           | Output                       | J2 - 14       |

| 9          | PMIC_PWRGOOD_LS            | Active high output signal from the module<br>to the expansion board that latches the<br>state of the module strapping options.<br>This signal also indicates if +VDD1 and<br>+VDD3 power supplies from the module<br>are within specification.                                                                                         | Output                       | J2 - 33       |

| 10         | SPI_1_CLK_LS               | SPI port 1 clock                                                                                                                                                                                                                                                                                                                       | Output                       | J2 - 53       |

| 11         | I2C_0_SDA_LS               | I2C port 0 data, used for configuration<br>EEPROM                                                                                                                                                                                                                                                                                      | Input/Output                 | J2 - 18       |

| 12         | I2S_1_RXD_LS               | I2S receive data                                                                                                                                                                                                                                                                                                                       | Input                        | J2 - 47       |

| 13         | I2C_0_SCL_LS               | I2C port 0 clock, used for configuration<br>EEPROM                                                                                                                                                                                                                                                                                     | Output                       | J2 - 57       |

| 14         | I2S_1_TXD_LS               | I2S transmit data                                                                                                                                                                                                                                                                                                                      | Output                       | J2 – 49       |

| 15         | ISH_I2C_0_SDA_LS           | I2C port 0 data, mapped to I2C5                                                                                                                                                                                                                                                                                                        | Input/Output                 | J2 - 18       |

| 16         | I2S_1_FS_LS                | I2S frame sync                                                                                                                                                                                                                                                                                                                         | Output                       | J2 - 45       |

| 17         | ISH_I2C_0_SCL_LS           | I2C port 0 clock, mapped to I2C5                                                                                                                                                                                                                                                                                                       | Output                       | J2 - 16       |

| 18         | I2S_1_CLK_LS               | I2S-bit clock supplied by the module in master mode and serves as an input in slave mode.                                                                                                                                                                                                                                              | Input/Output                 | J2 - 39       |

| 19         | ISH_I2C_1_SDA_LS           | I2C port 1 data, mapped to I2C6                                                                                                                                                                                                                                                                                                        | Input/Output                 | J2 - 23       |

| 20         | CODEC_MCLK_LS              | MCLK for Master Mode operation of I2S audio                                                                                                                                                                                                                                                                                            | Output                       | J2 - 43       |

| 21         | ISH_I2C_1_SCL_LS           | I2C port 1 clock, mapped to I2C6                                                                                                                                                                                                                                                                                                       | Output                       | J2 - 21       |

| 22         | UART_1_TXD_LS              | UART port 1 transmit data, hardware<br>strap with disable boot from eMMC<br>functionality                                                                                                                                                                                                                                              | Output                       | J2 - 28       |

| 23         | ISH_GPIO_6_LS              | General purpose input/output 6                                                                                                                                                                                                                                                                                                         | Output                       | J2 – 31       |

| J12<br>Pin | Net Name at<br>Breakout | Signal Description                                                                       | Default<br>Breakout<br>Usage | Module<br>Pin |

|------------|-------------------------|------------------------------------------------------------------------------------------|------------------------------|---------------|

| 24         | UART_1_RXD_LS           | UART port 1 receive data.                                                                | Input                        | J2 - 26       |

| 25         | ISH_GPIO_5_LS           | General purpose input/output 5                                                           | Output                       | J2 - 38       |

| 26         | PWM_0_LS                | Programmable pulse width modulator port 0                                                | Output                       | J2 - 1        |

| 27         | ISH_GPIO_4_LS           | General purpose input/output 4                                                           | Output                       | J2 - 29       |

| 28         | PWM_1_LS                | Programmable pulse width modulator<br>port 1                                             | Output                       | J2 - 3        |

| 29         | ISH_GPIO_3_LS           | General purpose input/output 3, set as output by BIOS until reconfigured <sup>2</sup>    | Output                       | J2 - 34       |

| 30         | PWM_2_LS                | Programmable pulse width modulator port 2                                                | Output                       | J2 - 22       |

| 31         | ISH_GPIO_2_LS           | General purpose input/output 2, set as output by BIOS until reconfigured <sup>2</sup>    | Output                       | J2 - 32       |

| 32         | PWM_3_LS                | Programmable pulse width modulator port 3                                                | Output                       | J2 – 24       |

| 33         | ISH_GPIO_1_LS           | General purpose input/output 1, set as<br>output by BIOS until reconfigured <sup>2</sup> | Output                       | J2 - 27       |

| 34         | +VDD1                   | System 1.8 VDC                                                                           | Output                       | J2 - 36       |

| 35         | ISH_GPIO_0_LS           | General purpose input/output 0; set as output by BIOS until reconfigured <sup>2</sup>    | Output                       | J2 - 25       |

| 36         | GND                     | System Ground                                                                            | Common<br>Ground             | Multiple      |

| 37         | GND                     | System Ground                                                                            | Common<br>Ground             | Multiple      |

| 38         | GND                     | System Ground                                                                            | Common<br>Ground             | Multiple      |

| 39         | GND                     | System Ground                                                                            | Common<br>Ground             | Multiple      |

| 40         | +VDD3                   | System 3.3 VDC                                                                           | Output                       | J2 - 30       |

UART\_0\_TXD is routed to a hardware-strapping pin on the Intel Joule module. Adding a pullup to this

net or loading it with external circuitry such that it is not at a valid low input voltage at the rising edge of

PMIC\_PWRGOOD, on start-up will result in disabling aspects of the Converged Security Engine (CSE)

which is responsible for retrieving and validating all firmware.

2. During BIOS execution, the ISH\_GPIO\_0 through \_3 signals are configured as outputs and change state to indicated BIOS progression. End users should take this into account in their design.

### 4.1.2 Breakout connector J13

The table below provides the pin assignment, signal name, and description for the signals on the breakout connector J13. The default breakout usage refers to the vantage point of the expansion board. For example, the SPI\_0\_MISO signal originates in the breakout board and is delivered to the expansion board, therefore it is an input.

These signals are mapped by various operating systems in different ways. These mappings can change over time and with BIOS updates. This table does not address those mappings. Refer to the Intel Joule module website for current mappings for supported operating systems.

| J13<br>Pin | Net Name at<br>Breakout | Signal Description                                                     | Default<br>Breakout<br>Usage | Module<br>Pin |

|------------|-------------------------|------------------------------------------------------------------------|------------------------------|---------------|

| 1          | GND                     | GND                                                                    | Common Ground                | Multiple      |

| 2          | V5P0V                   | 5V                                                                     | Output                       | N / A         |

| 3          | GND                     | GND                                                                    | Common Ground                | Multiple      |

| 4          | V5P0V                   | 5V                                                                     | Output                       | N / A         |

| 5          | GND                     | GND                                                                    | Common Ground                | Multiple      |

| 6          | V3P3V                   | 3.3V                                                                   | Output                       | N / A         |

| 7          | GND                     | GND                                                                    | Common Ground                | Multiple      |

| 8          | V3P3V                   | 3.3V                                                                   | Output                       | N / A         |

| 9          | GND                     | GND                                                                    | Common Ground                | Multiple      |

| 10         | V1P8V                   | 1.8V                                                                   | Output                       | N / A         |

| 11         | Reserved                | Reserved                                                               | Not used / Reserved          | J3 - 68       |

| 12         | V1P8V                   | 1.8V                                                                   | Output                       | N / A         |

| 13         | Reserved                | Reserved                                                               | Not used / Reserved          | J3 - 64       |

| 14         | GND                     | GND                                                                    | Common Ground                | Multiple      |

| 15         | Reserved                | Reserved                                                               | Not used / Reserved          | J3 - 58       |

| 16         | FLASH_TORCH             | GPIO Pin 7                                                             | Output                       | J3 - 75       |

| 17         | Reserved                | Reserved                                                               | Not used / Reserved          | J3 - 58       |

| 18         | FLASH_RST_N             | GPIO Pin 8                                                             | Output                       | J3 - 73       |

| 19         | SPI_0_FS0               | SPI port 0 slave select 0                                              | Input                        | J3 - 73       |

| 20         | FLASH_TRIGGER           | GPIO Pin 9                                                             | Output                       | J3 - 71       |

| 21         | SPI_0_FS1 <sup>2</sup>  | SPI port 0 chip select 1                                               | Output                       | J3 - 79       |

| 22         | AVS_M_DATA_1            | Microphone data for channels A and B                                   | Input                        | J3 - 66       |

| 23         | SPI_0_FS2               | SPI port 0 chip select 2                                               | Output                       | J3 - 53       |

| 24         | AVS_M_CLK_B1            | Microphone clock for channel B<br>(secondary microphone)               | Output                       | J3 - 62       |

| 25         | SPI_0_CLK               | SPI port 0 clock                                                       | Input                        | J3 - 59       |

| 26         | AVS_M_CLK_A1            | Microphone clock for channel A (voice trigger microphone)              | Output                       | J3 - 52       |

| 27         | SPI_0_MOSI              | SPI port 0 transmit data                                               | Output                       | J3 - 57       |

| 28         | UART_0_RXD              | UART port 0 receive data (Note:<br>UART_0_TXD is on the J12 connector) | Input                        | J3 - 51       |

#### Table 4. Breakout connector J13 pinout

| J13<br>Pin | Net Name at<br>Breakout | Signal Description                                             | Default<br>Breakout<br>Usage | Module<br>Pin |

|------------|-------------------------|----------------------------------------------------------------|------------------------------|---------------|

| 29         | SPI_0_MISO              | SPI port 0 receive data                                        | Input                        | J3 - 49       |

| 30         | UART_0_RTS              | UART port 0 ready-to-send                                      | Output                       | J3 - 55       |

| 31         | I2C_1_SDA               | I2C port 1 data                                                | Input/Output                 | J3 - 45       |

| 32         | UART_0_CTS              | UART port 0 clear-to-send                                      | Input                        | J3 - 47       |

| 33         | I2C_1_SCL               | I2C port 1 clock                                               | Output                       | J3 - 43       |

| 34         | ISH_UART_0_TXD1         | Although titled UART, function is configured as GPIO Pin 10    | Output                       | J3 - 15       |

| 35         | I2C_2_SDA               | I2C port 1 data                                                | Input/Output                 | J3 - 26       |

| 36         | ISH_UART_0_RXD          | Although titled UART, function is<br>configured as GPIO Pin 11 | Input                        | J13 - 13      |

| 37         | I2C 2 SCL               | I2C port 2 clock                                               | Output                       | J3 - 28       |

| 38         | ISH_UART_0_RTS1         | Although titled UART, function is<br>configured as GPIO Pin 12 | Output                       | J3 - 11       |

| 39         | PMIC_SLPCLK_1           | 32.768 kHz RTC                                                 | Output                       | J3 - 7        |

| 40         | ISH_UART_0_CTS          | Although titled UART, function is<br>configured as GPIO Pin 13 | Input                        | J3 - 9        |

ISH\_UART\_0\_TXD pin 34 and ISH\_UART\_0\_RTS pin 38 are routed to a hardware-strapping pin on the Intel Joule module. Adding a pullup to this net or loading it with external circuitry such that it is not at a valid low input voltage at the rising edge of PMIC\_PWRGOOD, on start-up will result in boot failure due to improper clock selection.

2. SPI\_0\_FS1, pin 21, is routed to a hardware-strapping pin on the Intel Joule module. Adding a pullup to this net or loading it with external circuitry such that it is not at a valid low input voltage at the rising edge of PMIC\_PWRGOOD, on start-up will result in boot failure due to boot halt being enabled.

§

# 5 **Powering the Expansion Board**

The Intel Joule expansion board is designed to accept power from either the DC barrel jack (J4) or the USB Type-C connector (J7). When both the DC barrel jack and USB power are applied, the board takes its power through the barrel jack by default.

When it is booted, the input source cannot be switched without rebooting the platform.

It is recommended to use the DC power input jack while developing on the platform because it is easier to ensure input power quality over a direct DC connection.

Any source connected to the J4 input must meet these specifications:

- Voltage: 12.0 volts, ±3%

- Current: 2.7 amps, minimum the expansion board contains a 3.5 amp fuse

- Safety Ratings: Listed LPS or Class 2

When using the USB Type-C as a power source, the developer must confirm the host system provides the required quality and capacity of input power. Excessive loads on a Type-C power bus can cause development platform and/or host instability.

As an Intel Joule-based project matures, the workload and platform power data can be used to guide an optimal power source that meets the intended form-factor goals.

### 5.1 DC power jack input (J4)

The J4 power jack on the expansion board is a surface mounted, RoHS compliant device. The connector is manufactured by CUI INC\* as model number: PJ-002AH-SMT-TR.

- The inner pin is positive voltage becoming the +VDC\_IN signal on the expansion board. The +VDC\_IN signal passes through a discrete circuit that provides polarity protection and filtering before reaching the input power multiplexer, U18.

- Outer ring is ground; this is common with module ground and connector shields.

- The jack accepts a 5.5 mm plug to a depth of 8.9 mm.

Refer to the manufacturer's datasheet for additional details and the latest information.

#### Table 5. DC power jack electrical specifications

| Source        | Item              | Min | Тур  | Max  | Units | Conditions                                |

|---------------|-------------------|-----|------|------|-------|-------------------------------------------|

| DC Power Jack | V <sub>DCIN</sub> | 7.0 | 12.0 | 12.4 | V     | At $V_{\text{DCIN}}$ pin of DC power jack |

|               | I <sub>DCIN</sub> |     |      | 2.7  | А     | At $V_{\text{DCIN}}$ of 12.0 volts        |

Note: Minimum voltage 7.0 is only for lightly loaded configurations. Attaching accessories will require the more typical voltage of 12.0.

# 5.2 USB Type-C power input (J7)

The J7 Type-C connector accepts a 5 VDC level and is capable of delivering a maximum of 3 A into the expansion board. J7 pins A4, B4, A9 and B9, are +VBUS; J7 pins A1, B1, A12, B12 are ground.

The 4 positive voltage input lines are common on the expansion board and become +VBUS\_USB3, which is conditioned to become +VBUS going into the power mux.

+VBUS is also connected to the module at J3 pin 1 as the USB adapter connection sense line.

When powering the expansion board from a USB PD charger/adaptor only capable of 5 volt output, workloads executing must not exceed a total current consumption of 3.0 amps, including any mezzanine boards and peripheral devices attached to it.

When powering the expansion board from a USB PD charger/adaptor capable of 9 volt output, the BIOS automatically negotiates PD output voltage from 5 volt to 9 volt operation.

| Source              | Item              | Min  | Тур | Max  | Units | Conditions                                  |

|---------------------|-------------------|------|-----|------|-------|---------------------------------------------|

| Type-C<br>Connector | V <sub>BUS1</sub> | 4.75 | 5   | 5.25 | V     | At $V_{\text{BUS}}$ pin of Type-C connector |

|                     | I <sub>BUS1</sub> | 3.0  |     | 3.5  | А     |                                             |

|                     | V <sub>BUS2</sub> |      | 9   | 12.4 | V     | At $V_{\text{BUS}}$ pin of Type-C connector |

|                     | I <sub>BUS2</sub> | 1.5  |     | 3.5  | А     |                                             |

#### Table 6. USB type-C power input electrical specifications

The USB power system, OTG, and interface details are covered in Section 15.1.

### 5.3 Battery path

There are four (4) through-hole connection points near the J4 VDC input connector; a +VBATTERY trace begins here and is routed to the power management device, EU2.

Note: No battery enabling, charging, or support services are currently provided by the expansion board.

All battery solutions must be completely external to the expansion board except for standard communication and I/O interfaces. The EU2 device serves as the +VSYS voltage regulator.

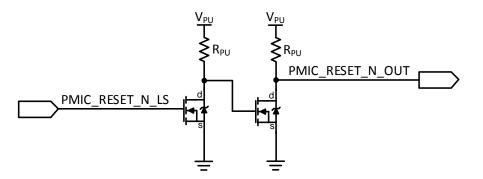

## 5.4 Power-on and shut-down signaling